شرکت Samsung Foundry اعلام کرده که تولید انبوه تراشههای نسل اول خود را بر روی گره ۳ نانومتری آغاز کرده است. این پروسه براساس معماری جدید ترانزیستور یعنی (GAA (Gate All Around است که گام بعدی پس از FinFET است.

در مقایسه با فرآیند ۵ نانومتری، تراشههای نسل اول ۳ نانومتری سامسونگ میتوانند تا ۲۳ درصد عملکرد بهتر، تا ۴۵ درصد کاهش مصرف انرژی، و ۱۶ درصد کاهش سطح را ارائه دهند. گره ۳ نانومتری نسل دوم سامسونگ حتی از این هم چشمگیرتر خواهد بود، سامسونگ ادعا میکند که این نوع گره در مقایسه با فرآیند ۵ نانومتری، به کاهش ۵۰ درصدری مصرف انرژی، تا ۳۰ درصد بهبود عملکرد، و کاهش ۳۵ درصدی مساحت دست خواهد یافت که اگر واقعا صحت داشته باشد پیشرفت بسیار خوبی محسوب میشود.

در این مورد اکنون سامسونگ از TSMC جلوتر است، زیرا انتظار میرود که TSMC تولید انبوه تراشههای ۳ نانومتری خود را در نیمه دوم امسال آغاز کند، اما در مورد کیفیت تراشهها فعلا نمیتوان نظری داد و سامسونگ را برتر دانست، زیرا سابقه این شرکت نشان میدهد که گرچه ممکن است در مواردی مانند تولید زودتر با فرآیندهای جدید پیشرو باشد، اما کیفیت تراشههای آن در شرایط یکسان، در اغلب موارد از TSMC پایینتر بودهاند.

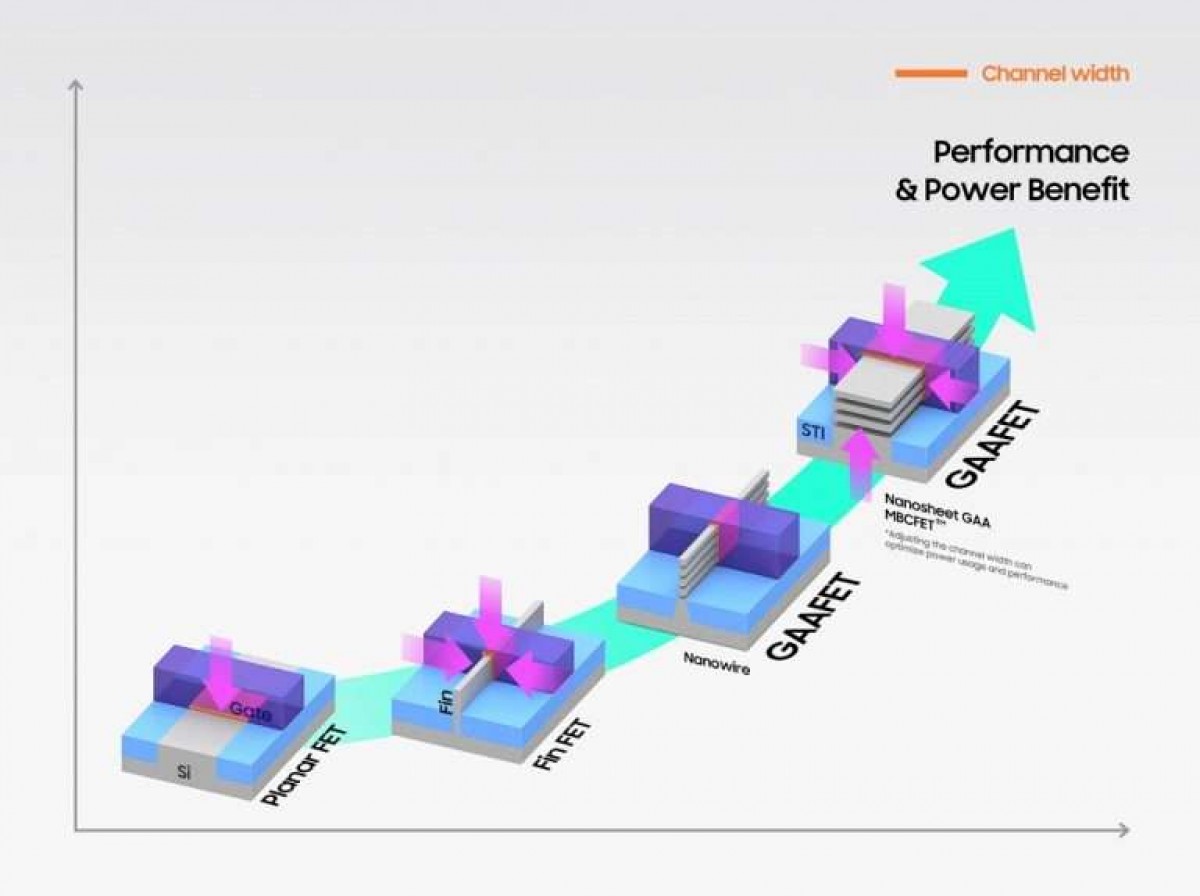

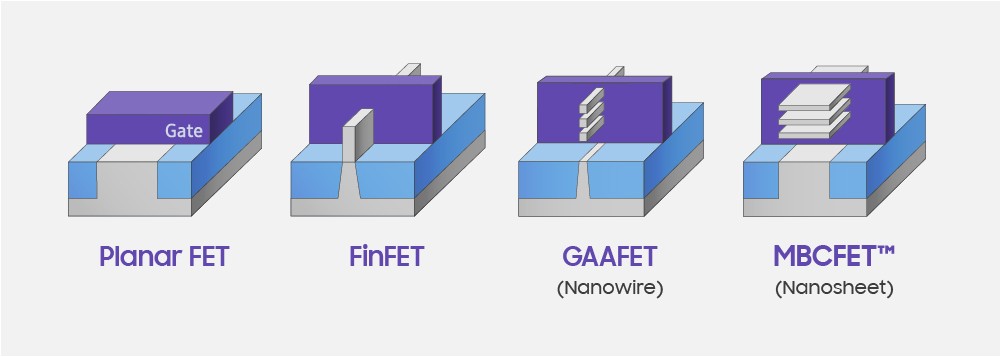

طراحی ترانزیستور GAA یا Gate All Around به کارخانه تولید تراشه اجازه میدهد تا ترانزیستورها را کوچک کند، بدون اینکه به توانایی آنها در حمل جریان آسیبی وارد شود. طراحی GAAFET مورد استفاده در گره ۳ نانومتری، ناشی از فنآوری MBCFET است که در تصویر زیر نشان داده شده است.

سیر تکاملی ترانزیستورهای سیلیکونی

نظرات(0)