TSMC جدول زمانی تولید تراشههای خود را با فرآیند ۲ و ۳ نانومتری اعلام کرد

تبلیغات

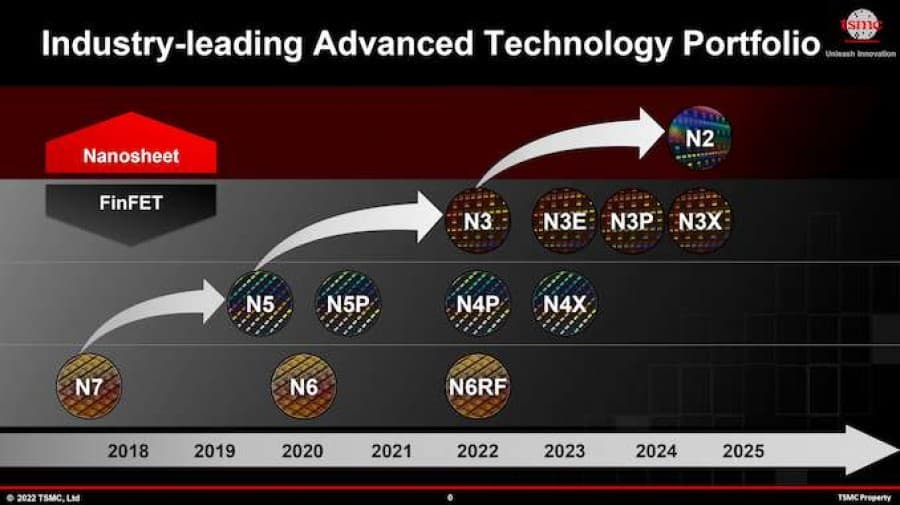

شرکت TSMC جدول زمانی توسعه تراشههای خود را در نشست فناوری سال ۲۰۲۲ خود شرح داد. این سازنده تراشه مستقر در تایوان، تراشههای ۳ نانومتری را در نیمه دوم سال جاری معرفی میکند و فناوری ۲ نانومتری را در سال ۲۰۲۵ به صحنه جهانی خواهد آورد.

گره ۳ نانومتری در ۵ طبقه عرضه خواهد شد که هرکدام قدرتمندتر، با ترانزیتورهای متراکمتر و کارآمدتر هستند، این ۵ گروه عبارتند از:

- N3

- (N3E (Enhanced

- (N3P (Performance Enhanced

- (N3S (Density Enhanced

- (N3X (Ultra High Performance

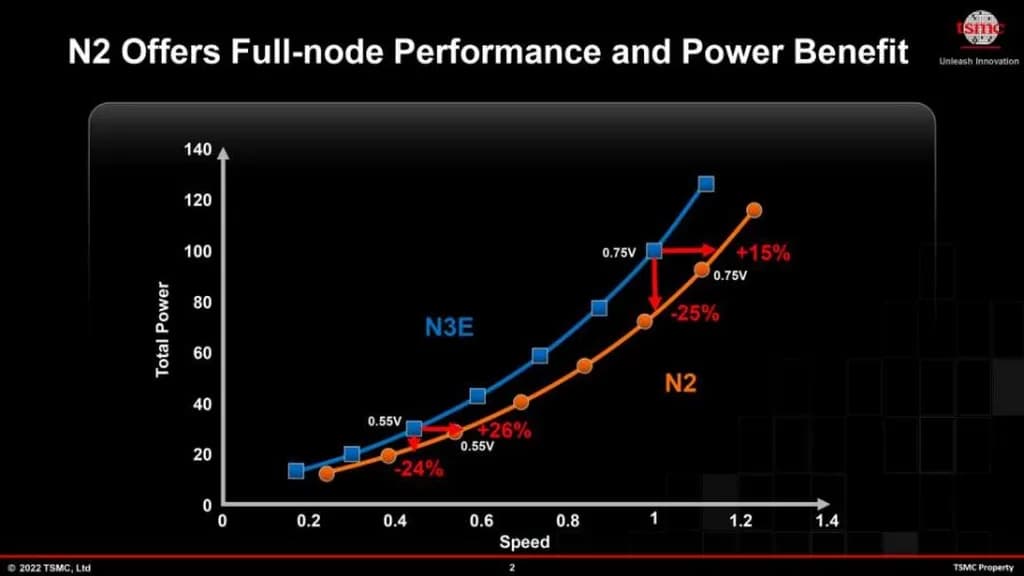

در گره ۲ نانومتری در مقایسه با گره N3E، عملکرد پردازنده ۱۰ تا ۱۵ درصد با توان مصرفی یکسان افزایش مییابد و ۲۵ تا ۳۰ درصد مصرف انرژی کمتر را در همان فرکانس و تعداد ترانزیستور شاهد خواهیم بود. N2 یا همان فرآیند تولید ۲ نانومتری هم چگالی تراشه را نسبت N3E، به میزان ۱٫۱ برابر افزایش میدهد.

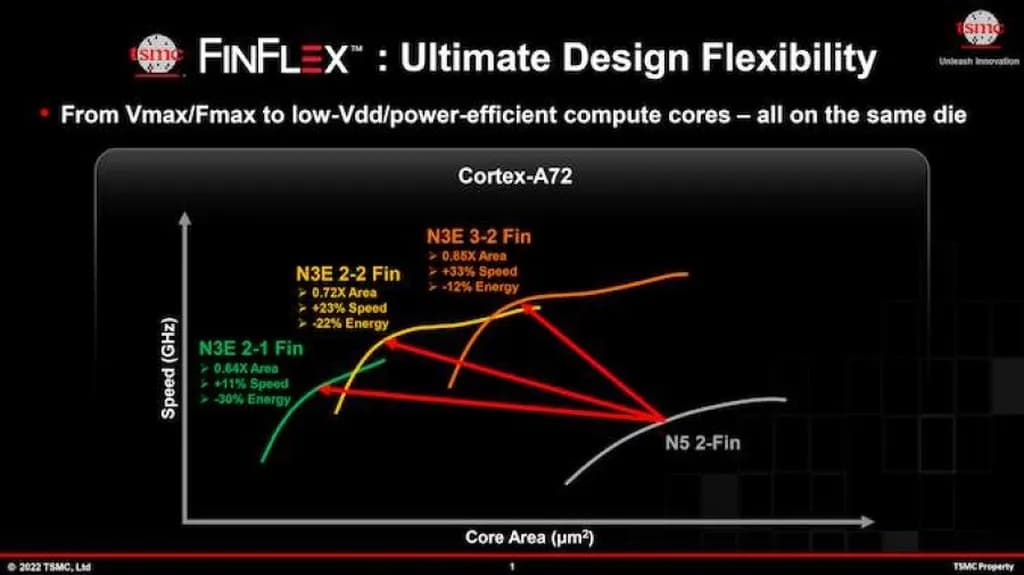

همچنین TSMC فرآیند GAAFET یا همان ترانزیستورهای اثر میدانی همه جانبه را معرفی کرد. این ترانزیستورهای نانو صفحه جدید با کاهش مقاومت، عملکرد در هر وات را افزایش خواهند داد.

در همین حال شرکت Samsung Foundry نیز تولید انبوه تراشههای ۳ نانومتری را در سال جاری آغاز خواهد کرد، اما قصد دارد تولید تراشههای ۲ نانومتری را در سال ۲۰۲۵ آغاز کند.

جدای از اینکه رقابت در این حوزه بسیار هیجان انگیز است، فکر اینکه در نهایت در سالهای آینده چه بر سر فرآیندهای تولید تراشه پس از رسیدن به گره ۱ نانومتری میآید، واقعا غیر قابل پیش بینی به نظر میرسد؛ شکی نیست که در آینده تولید تراشه نیاز به تحولی بنیادین پیدا خواهد کرد، حال باید دید که در سالهای آتی این تحول به چه سمت و سویی خواهد رفت.